## Article

# A Model-Driven Co-design Framework for Fusing Control and Scheduling Viewpoints

# Sakthivel M Sundharam <sup>1</sup>\*<sup>(b)</sup>, Nicolas Navet <sup>1</sup>, Sebastian Altmeyer <sup>2</sup><sup>(b)</sup> and Lionel Havet <sup>3</sup>

- <sup>1</sup> Laboratory of Advanced Software Systems (LASSY), CSC Research Unit, University of Luxembourg, Maison du Nombre, L-4364 Esch-sur-Alzette, Luxembourg;

- E-mails: sakthivel.sundharam@uni.lu; nicolas.navet@uni.lu

- <sup>2</sup> CSA Group, University of Amsterdam, 1098XH Amsterdam, Netherlands; altmeyer@uva.nl

- <sup>3</sup> RealTime-at-Work (RTaW), 4 Rue Piroux, 54000 Nancy, France; lionel.havet@realtimeatwork.com

- \* Correspondence: sakthivel.sundharam@uni.lu; Tel.: +352-466-644-5132

Academic Editor: name Version February 8, 2018 submitted to Sensors

- Abstract: Model-Driven Engineering (MDE) is widely applied in the industry to develop new

- <sup>2</sup> software functions and integrate them into the existing run-time environment of a Cyber-Physical

- <sup>3</sup> System (CPS). The design of a software component involves designers from various viewpoints such

- as control theory, software engineering, safety, etc. In practice, while a designer from one discipline

- focuses on the core aspects of his field (for instance, a control engineer concentrates on designing

- <sup>6</sup> a stable controller), he neglects or considers less importantly the other engineering aspects (for

- <sup>7</sup> instance, real-time software engineering or energy efficiency). This may cause some of the functional

- and non-functional requirements not to be met satisfactorily. In this work, we present a co-design

- framework based on timing tolerance contract to address such design gaps between control and

- <sup>10</sup> real-time software engineering. The framework consists of three steps: controller design, verified by

- jitter margin analysis along with co-simulation, software design verified by a novel schedulability

- <sup>12</sup> analysis, and the run-time verification by monitoring the execution of the models on target. This

- framework builds on CPAL (Cyber-Physical Action Language), an MDE design environment based

- on model-interpretation, which enforces a timing-realistic behavior in simulation through timing

- and scheduling annotations. The application of our framework is exemplified in the design of an

- automotive cruise control system.

- Keywords: model-driven engineering; control software; timing tolerance contract; controller model;

- schedulability; stability; input jitters; varying execution-times; output jitters; input-to-output delay;

- <sup>19</sup> co-simulation; real-time scheduling; control system performance

## 20 1. Introduction

Control theory and software engineering are two disciplines involved in the development of 21 control software. Traditionally, control engineers design the controller model without considering 22 the computing platform constraints and specifications. The converse applies to software engineering, 23 where control performance is not considered during software design. The control engineering and 24 the software engineering are two different worlds with different objectives in mind. Consequently, 25 the complete set of functional and non-functional requirements of the control software are usually 26 not elicited at the control design stage. Hence, as discussed in [1], substantial design-gaps may exist 27 during the design of a control software. 28

<sup>29</sup> The control software executes on an Electronic Control Units (ECU) interfaced with various

<sup>30</sup> sensors and actuators. The continuous-time signals are periodically sampled; each sampled set of data

is then processed by real-time control functions. Control theory typically assumes deterministic and 31 periodic sampling. However in practice, for instance, due to preemptions and varying task execution 32 times, there exists a varying delay between sensing and actuation, which is called input-to-output 33 delay or sensing-to-actuation delay. A control designer typically assumes this input-to-output delay 34 to be zero or constant which is an unrealistic assumption. The input-to-output delay depends on the 35 time at which sensing and actuation takes place. Sensing time may also vary over time typically due 36 to the interference of higher priority tasks, and the variability of sensing times is called *input jitter*. 37 There are also jitters in the actuation times, called *output jitters* caused by varying execution times and 38 preemptions. These jitters directly impact the quality of control functions, and, in the worst-case, they 39 might jeopardize the safety of the system. Hence, it is important to consider these delays during the 40 design phase of the control software. This work addresses the case where the input data acquisition is 41 done locally on one node. It can be extended like in TrueTime [2] to cover the case of networked control 42 systems, including "Industrial Internet of Things" (IIoT) applications, where data are transmitted over 43 a network, which would increase the input jitters, as well as the input-to-output delays.

#### 45 State-of-the-art

A survey of tools and methods developed to address this problem is presented in [3]. Most of 46 the techniques discussed in this survey are based on co-design approaches. Directly relevant to our work are TrueTime [2] and T-Res [4] which are simulation tools that can consider how the timing 48 behavior of the implementation affects the performance of the control. Both approaches use Simulink 49 for control design and timing extension toolboxes to include computing aspects, foremost the effects 50 of task scheduling on the control performance. In a recent study [5], we discussed our co-design and 51 simulation environment and compared it with these state-of-the-art tools. Our co-design technique mainly differs from these approaches by allowing the control model to be directly executed (by an 53 interpreter engine) on the target hardware, without changing a single line of code. The benefits are 54 reduced development time and avoidance of distortions (i.e., semantic gaps) between the simulated 55 and executed control programs. On the other hand, TrueTime and T-Res are essentially simulation 56 environments that involve a step of model-to-code transformation (typically code generation), which may risk widening the semantic gap between model and executable code, requiring additional development effort. Generally speaking, the existing co-design simulation techniques are mainly 59 concerned with enabling the study of the effect of timing variabilities on control performance, rather 60 than addressing the design gaps between control and software viewpoints. Other works [1,6] present 61 co-engineering techniques where the initial controller is integrated in a virtual ECU. The behavior 62 of the controller is then assessed through timing analysis tools whose results are injected into the 63 controller model. This approach shares similarities with ours but it relies on expensive and proprietary 64 timing analysis tools and remains at the model level (i.e. implementation is abstracted). 65

#### 66 Contribution

In this paper, we propose a framework that supports our co-design modeling environment for 67 both controller and control software development. The framework provides schedulability and control 68 performance analysis along with simulation capabilities. We underpin the proposed framework with 69 the help of timing contracts introduced in [7] which are sets of timing characteristics that ensure the 70 targeted control performance. The timing contract can be a crucial concept in component-based design because it drives and synergizes the design thinking of the stakeholders from different viewpoints. 72 We use the timing contract as a candidate to bridge the control software design-gaps. During the 73 application of a timing contract, we observe a vertical type contract [8] in our proposed framework as 74 the timing contract is applied between two phases of the Software Development Life Cycle (SDLC), in 75 this case between controller design and software development. 76

The co-design framework presented in this work encompasses three steps of the development cycle: (i) controller design, (ii) software scheduling and execution platform configuration, and (iii)

run-time monitoring. Firstly, we discuss scheduling and stability viewpoint analyses supporting 79 the proposed co-design and simulation environment. We rely on our timing-aware model-driven 80 environment called Cyber-Physical Action Language (CPAL) for co-design in Simulink. We then 81 present the CPAL constructs and timing annotations, central to our approach, which enable us to 82 reproduce the timing irregularities of interest, such as jitters and varying input-to-output delays. 83 CPAL provides the timing dimension to the controller design, which acts on the plant model in 84 Simulink. We provide the CPAL execution platform for Simulink as open access for experimentation. Along with existing jitter analysis tools, the proposed co-design platform helps designing stability guaranteed controller models by integrating the target-platform timing behavior. Furthermore, it 87 provides software engineering with the control information needed to bound the space of feasible 88 software design solutions. The stability verification itself is done with the help of the jitter margin 89 concept and the co-simulation of CPAL execution in the Simulink environment. 90 The second contribution is the verification of the timing tolerance contract assumptions made

during controller design. The verification is specifically useful when a new control function is 92 integrated into an existing stable and functioning ECU. How can we analytically validate whether the 93 system maintains the desired performance (stable and schedulable) after integration? To this end, we 94 propose a novel schedulability analysis for a certain class of task and execution models in real-time 95 scheduling. To assign a realistic execution time to the controller task, we estimate the Worst-Case 96 Execution Time (WCET) beforehand using measurements of the model running on the target hardware. 97 The third and last contribution is the proposed run-time verification methodology. During model 98 on target execution, we check whether the newly integrated controller function stays within the 99 stability margin. For this, we take advantage of CPAL introspection features to monitor the execution 100 characteristics of a controller model at run-time. More specifically, we introspect whether the jitters and 101 input output latencies are within the margin guaranteeing the stability and schedulability objectives. 1 02

## 103 Structure

This paper is structured as follows. In Section 2, we explain the system model and the steps 104 involved in the framework for fusing control and scheduling viewpoints. Section 3 presents the 1 05 proposed co-modeling and simulation environment as well as jitter analysis tools and methods. In 106 Section 4, we explain the verification of timing tolerance assumptions using WCET measurements and 107 the schedulability analysis. In Section 5, we evaluate the framework using the example of a cruise 108 control system. In the same section, we discuss the stability verification using the jitter margin concept 109 and the CPAL co-simulation in Simulink. The section also details the scheduling configuration and 110 run-time introspection features. Section 6 provides the related work. Section 7 concludes the paper. 111

## 112 2. Framework for Fusing Control and Scheduling Viewpoints

System designers in the industry are typically highly knowledgeable in their own fields (control systems, software engineering, scheduling, etc.) but contracts among design teams are not necessarily well established and communicated amongst the stakeholders. Our objective is to define a structured framework, with clear interfaces, which can be agreed upon and followed by all. The framework proposed in this section highlights the issues faced at each step of the design and we propose possible solutions. Our framework may not be suitable for all industrial settings, but it addresses the gap between control models and their implementation, and can serve as a basis for context-specific design frameworks.

## 121 2.1. System Model

We propose an integrated framework which combines the tools and methods necessary to design a model of the system. Table 1 provides a quick reference for the notations used in this paper. The system is comprised of a controller model, a plant model and platform model. Plant *P* is modeled by a continuous-time system of equations

$$\dot{x} = Ax + Bu,

y = Kx,$$

(1)

where *x* is the plant state and *u* is the control signal. The plant output *y* is sampled periodically with some delays at discrete time instants. The control signal is updated periodically with some delays at discrete time instants, (i.e., actuation also happens with some delay). Quantities *A*, *B*, *K* are constants. The controller model is comprised of a task set  $\Gamma$  of *n* periodic tasks { $T_1, \ldots, T_n$ } executing on a single processor.

| task-set                                               | $\Gamma = \{T_1, \ldots, T_n\}$            |

|--------------------------------------------------------|--------------------------------------------|

| pseudo task-set                                        | $\Gamma = \{\hat{T}_1, \dots, \hat{T}_n\}$ |

| number of tasks                                        | $n \in N$                                  |

| job index                                              | i, j e N                                   |

| task worst-case execution time with no interference    | $C_i \in R$                                |

| task period                                            | $h_i \in R$                                |

| task relative deadline                                 | $D_i \in R$                                |

| task absolute deadline                                 | $d_i \in R$                                |

| task release time                                      | $r_i \in R$                                |

| task finish time                                       | $f_i \in R$                                |

| task worst-case response time                          | $R_i^w \in R$                              |

| task best-case response time                           | $R_i^b \in R$                              |

| task processor demand                                  | $PD_i \in R$                               |

| task busy-period                                       | L & R                                      |

| input jitter also known as sampling jitter             | $J^h \in R$                                |

| output jitter also known as response-time jitter       | $J^{\tau} \in R$                           |

| input-to-output delay also known as <i>StA</i> latency | τεR                                        |

| k-th sensing time instance                             | $t_k^s \in R$                              |

| k-th actuation time instance                           | $t_k^{\tilde{a}} \in R$                    |

| nominal input-output delay                             | $\hat{\mathfrak{L}} \in R$                 |

**Table 1.** Notations used in the paper

Each controller task  $T_i$  is represented by a tuple  $T_i: (O_i, C_i, h_i, D_i)$ , where  $O_i$  is the task's release offset,  $C_i$  the Worst-Case Execution Time (WCET),  $h_i$  the task's period and  $D_i$  the deadline.  $R_i^{w}$  and  $R_i^{b}$ are the worst and best-case response times. The task instances, also referred to as jobs, are scheduled non preemptively in order of their arrival. Each controller task is assumed to have three activities in the order sensing, computation and actuation. Sensing is the first activity which *reads* the data from a sensor. The computation also known as *control law execution* is the second activity. The actuation is the last activity which *writes* the data to physical devices.

The variability in the times at which the control software reads and writes the input and output data is called jitter. Jitters have a major impact on the performance of some control systems. To formally define the jitters that must be respected by an execution platform, the authors in [7] introduce four timing contracts namely Zero Execution Time (ZET), Bounded Execution Time (BET), Logical Execution Time (LET) and Timing Tolerance (TOL) contract. In this work, we consider the latter contract which is more general than ZET and BET, and does not imply strong implementation constraints like LET [9]. A Timing Tolerance TOL contract implies that the following conditions hold:

$$\begin{aligned} t_k^s & \in [k.h, k.h + J^h], \\ t_k^a & \in [t_k^s + \tau - J^\tau, t_k^s + \tau + J^\tau], \end{aligned}$$

$$(2)$$

where  $J^h$  is the tolerable input jitter.  $\tau$  is the tolerable input-to-output delay also known as tolerable

<sup>139</sup> Sensing-to-Actuation delay (StA delay). The nominal input-to-output delay  $\mathfrak{L}$  is a minimum delay

experienced between input to output.  $J^{\tau}$  is the tolerable output jitter. The tolerances  $J^{h}$  and  $J^{\tau}$  are also referred to as margins, namely input jitter margin and output jitter margin.

## 142 2.2. Framework Steps

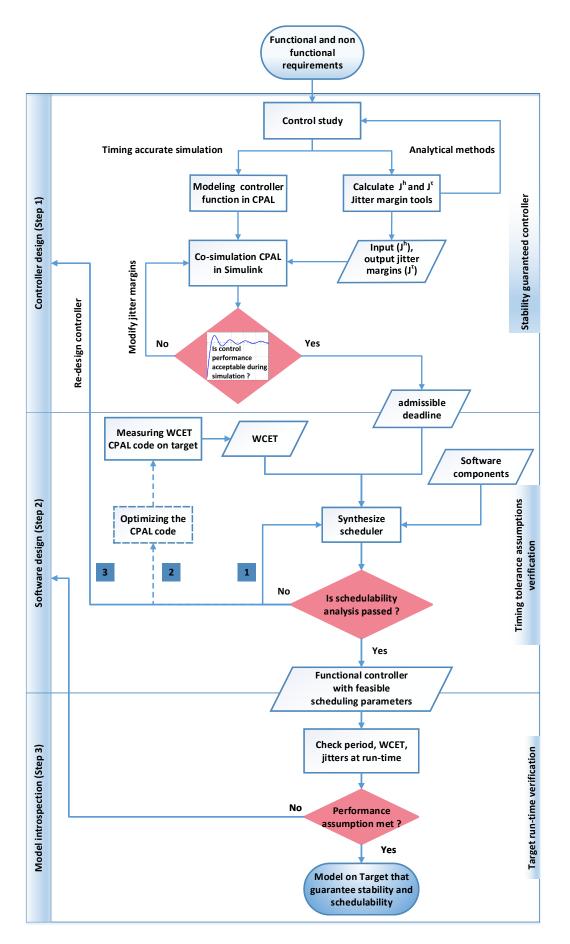

To bridge the control-computing gap, we propose a framework that fuses the control and scheduling viewpoints in the context of model-based system design. Figure 1 shows the overall step-by-step flow of the framework.

## 146 Step 1 : Controller Design

Based on the functional and non-functional requirements, the first stage of the framework is the control study, that determines the control equations that will potentially allow the system to achieve the required control performances. This control study relies on the designer's expertise with the help of control-system simulators like MATLAB/Simulink, which include the plant model. We note that at this stage the timing issues are not considered, and in particular the implementation delays are ignored, which may require to revisit the choice of the control law later in the design flow.

The next stage is to model the control law in CPAL, which provides native support for Finite State Machines (FSMs) to describe the logic of the algorithm, in a similar way as StateFlow. The CPAL 1 54 model controls the plant model designed in the Simulink environment. At this stage, timing delays are 155 introduced : the controller tasks are activated with input-to-output delays using timing annotations in 156 the CPAL model (input and execution time jitter). The timing annotations are also useful for defining 157 tasks' periods, deadlines, priorities of execution, and the scheduling policy. The CPAL interpreter, which can be seen as an execution engine, runs the controller model within the Simulink environment 159 that hosts the CPAL/Simulink co-simulation. The simulation results such as control performance, task 1 60 activation diagram and values of the outputs are all available within Simulink. 161

As discussed in [10], the controller design can be done using two analytical methods: expected 1.62 control performance and worst-case control performance. The Jitterbug toolbox [11] is used to calculate 163 the expected value of quadratic control costs. The Jitter margin toolbox is used to calculate the worst-case control cost, as explained in details in Section 5.2.1. For a given control performance, this 165 tool determines the tolerable jitter margins. In turn, these jitter margins provide admissible deadlines 166 for the controller tasks. Using the proposed co-simulation, we verify the tolerable input jitter margin 167  $I^n$  and tolerable input-to-output delay (StA delay) under which the system maintains an acceptable 168 stability performance. We also fine-tune the obtained deadline for step response expectations when 169 required. Further, using simulations, we study the effect of these tolerable jitter margins on control 170 performance. 171

## 172 Step 2 : Software Design

At the end of step 1, each controller model consists of a single task performing sensing, 173 computation and actuation. Note that this task can be integrated with other existing tasks ("Software 174 components" block in 1). At step 2, a suitable scheduling solution, i.e., a scheduling policy and the 175 associated parameters should be selected so as to meet the real-time constraints expressed as deadlines 176 derived at the first step. This can be achieved, for instance, using the optimization framework in [12], 177 a form of scheduler synthesis. Schedulability analysis has to be performed under some Worst-Case Execution Time (WCET) assumptions for all tasks. These values can be obtained by analysis or, as in 179 our approach, approximated with on-target measurements. If this scheduling configuration meets the 180 timing performance needed to provide the necessary control performance to the controller task then 181 the design flow moves on to step 3. Otherwise, we return to step 1 and redesign the control law. 182

**Figure 1.** Illustration of framework flow for fusing control and scheduling viewpoints. The dashed part in the software design step is out-of-scope of this paper.

The same CPAL model executed in the simulation environment (in the previous step) is now interpreted directly on the target to measure the execution time of the task. Schedulability analysis can then be performed, and we propose a novel schedulability analysis for FIFO policy with offsets in Section 4. Although FIFO is outperformed by most policies in terms of meeting deadlines [13], it has the advantage that the scheduling order does not depend on the execution times, irrespective of the platform. The schedulability analysis checks whether the controller task we integrate with the existing software components remains schedulable or not.

This stage, if successful, ensures that the timing constraints coming from the control laws are met by the software and execution platform. If unsuccessful, we can first try to optimize the CPAL code. This may include breaking down the controller task into sub-tasks, for instance one for sensing, one for computation and one for actuation, which is a classical strategy to increase the schedulability of control systems [14], but in some cases the suitable strategy has to be specific to the application. If still unsuccessful, the process returns to step 1 for a redesign or fine-tuning of the controller. In any cases, the model used at step 1 for functional simulation will be the one used for execution on the target hardware.

## 198 Step 3 : Model Introspection

From step 2, we obtain a functional CPAL controller along with the scheduling parameters to be configured for on-target execution. These parameters have been derived from the models. To make sure that there is no distortion between the model's assumptions and the execution, task characteristics such as period, offset, jitter, priority, deadline as well as the activation time of the current and previous instances are monitored during execution using the CPAL introspection features. In Section 5, we discuss the monitoring of CPAL model execution at run-time, especially the monitoring of timing tolerance specifications such as input jitters, output jitters and the input-to-output delays.

## 206 3. Analysis and Co-simulation of Controller Design

This section explains the controller design using analytical methods and co-simulation. The result of this stage is a controller whose stability and more generally performance are guaranteed under certain assumptions on the worst-case timing behavior of the software implementation.

## 210 3.1. Jitter Analysis

Jitter analysis is performed using two evaluations, namely the evaluation of the expected control 211 performance, and of the worst-case control performance. For instance, the Jitterbug toolbox [11] can be 212 used to calculate the expected value of quadratic control costs. This measure in the general case is not 213 sufficient to guarantee the stability of the plant [10], but stability can be verified through worst-case 214 control performance analysis. In our framework, the technique presented in [15] and implemented in 215 the jitter margin toolbox is used for the derivation of the jitter margins, both input and input-to-output 216 delays, ensuring stability under the worst-case control performance. The calculated jitter margins 217 imply the maximum deadline for a controller task. This theoretical bound on the deadline derived by 218 analysis may be further fine-tuned by simulation as explained in the next subsections. 219

## 220 3.2. Controller Modeling in CPAL

CPAL, short for Cyber-Physical Action Language, is a modeling and discrete-event simulation language for cyber-physical systems [16]. CPAL serves as a design-exploration platform with graphical representation. The models can be executed both in simulation mode as well as in real-time mode on an embedded target. CPAL is a lightweight execution engine (around 10000 lines of C code) designed for timing predictability that can run on top of an OS or without any OS, and thus without the interferences the OS would create.

In case of simulation, execution is as fast as possible according to a logical clock and not the physical time (see [17]). Typically, executing in simulation mode is several orders of magnitude faster

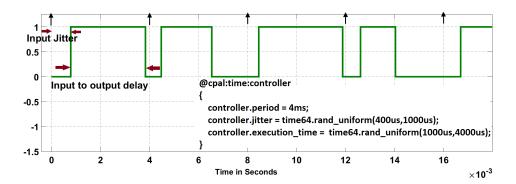

than in real-time mode. The controller code executes in zero-time during simulation, except if it uses 229 predefined CPAL timing annotations. The simulation mode CPAL interpreter is an execution engine 230 hosted by an operating system. The simulation execution can be carried out in a stand-alone built-in 2 31 simulation environment [18] or it can be used in co-simulation environments, for instance as in this 232 work integrated in MATLAB/Simulink as an S-function. CPAL aims to achieve the same temporal 233 behavior in simulation mode and real-time mode on the target. This property is referred to as *timing* 234 *equivalence*. It can be achieved through timing annotations to inject delays in the simulation model. 235 Figure 2 illustrates the CPAL timing annotations to inject input and output jitters in a control model. 236

**Figure 2.** Simulating random input and output jitters affecting a CPAL controller model using timing annotations. Level 1 means that the controller is being executed.

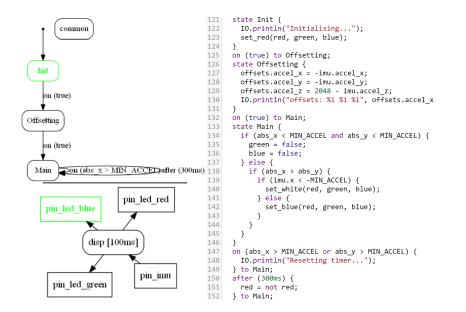

Like other modeling environments for control programs such as StateFlow, CPAL provides 237 support for Finite State Machines (FSMs) with conditional and timed transitions. As can be seen 238 in Figure 3, transitions can happen either when a boolean condition is true, after a certain time 239 duration is spent in the active state, or the conjunction of both. A distinctive feature of CPAL is that 240 it relies on model interpretation: a CPAL model verified by simulation can be executed directly on 241 an embedded target such as ARM Cortex - M4 (FRDM K64F) and ARM Cortex - A7 (Raspberry 242 Pi). Model-interpretation is well suited for rapid-prototyping [19] and prevents any distortion 243 between models and code that could be introduced during code generation. A disadvantage of model interpretation is that it is slower than compiled code. For that reason, it is not always a practical 245 solution for on-target execution. For the purpose of simulation on desktop machines, the execution 246 time of the control part is however not an issue, especially in a co-simulation environment where 247 simulating the plant is by far the most time-consuming task. 248

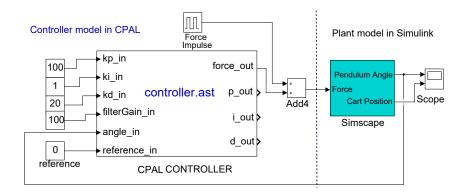

The CPAL documentation, a graphical editor and the execution engine for various desktop and embedded platforms are freely available at http://www.designcps.com. The CPAL control library as in Figure 4 needed to execute in MLSL controller models written in CPAL, and the models to reproduce the experiments of this paper are freely available at https://www.designcps.com/wpcontent/uploads/cpal\_codesign\_framework.zip.

#### 254 3.3. Co-simulation in MATLAB/Simulink

In our proposed co-simulation approach, a controller model is designed in CPAL, and the plant 255 model in Simulink. Controllers can easily be designed in Simulink too. But Simulink out-of-the-box 256 is not offering possibilities to study the performance of control loops subject to scheduling and 257 258 networking delays. Indeed, varying execution times, preemption delays, blocking delays, kernel overheads cannot be captured in the standard Simulink environment. This can be done only with 259 TrueTime [2], which, to the best of our knowledge, is the most widely used tool in the real-time and 260 control communities to study control performance subject to timing irregularities. One should also cite 261 T-Res [4], a more recent and modular version of TrueTime. 262

**Figure 3.** CPAL program illustrating the native support for FSM, conditional and timed state transitions. The top-left graphic is the representation of the FSM embedded in a process, while the bottom-left graphic is the functional architecture with the flows of data, as both seen in the CPAL-editor.

**Figure 4.** Controller model for an inverted pendulum integrated within the Simulink environment. Input data of the controller are visible in the design window and can be changed without the need to access the CPAL model. The output data are updated by the CPAL controler. The controller model is written in CPAL and executed by an interpreter embedded in the controller block. The *ast file* format is the more-compact binary equivalent form of the source-code controller model.

In [5], we have discussed how to integrate the timing behaviour of the controller into Simulink 263 models. In this work, we have studied how CPAL timing-accurate interpretation in Simulink compares 264 against TrueTime and T-Res. The important difference, and also the advantage of our co-modelling 265 approach is that the same model used during simulation can be used on target, whereas TrueTime 266 and T-Res are simulation environments. Also, like Simulink, CPAL is a high-level embedded systems 267 specific language which favors productivity and correctness by providing domain-specific constructs 268 and abstractions [20]. In the case of the co-simulation of CPAL within MLSL, Simulink acts as the 269 primary simulator while CPAL executes the controller model as an S-function, and is being called 270 by the Simulink engine. The S-functions (system-functions) are high-level programming language 271 description of a Simulink block written in C, C++ etc. The CPAL control library is implemented as a 272 mex (Matlab Executable) file, which executes the CPAL controller model. This CPAL controller is a 273 generic execution engine that can run any CPAL model. Before execution, the CPAL source model 274 is converted into a binary-equivalent representation (an Abstract Syntax Tree, shortly ast file format) 275

- using the CPAL parser. The Simulink engine interacts with the CPAL model through data flows and

- <sup>277</sup> control flows. Data flow, for instance *force\_out* in Figure 4, are used for the exchange of information

- <sup>278</sup> between the Simulink engine and the CPAL controller, while the control flows define when Simulink

- <sup>279</sup> invokes the CPAL S-function.

```

1 include controller.cpal

2  /* periodic process with initial offset, 10ms is period, 2ms is offset */

3 process PIController: invertedPendulumController[10ms,2ms](kp_in, ki_in, kd_in,

4  filterGain_in, angle_in, reference_in,

5  force_out, p_out, i_out, d_out);

6 /* annotations of task timing parameters */

7 @cpal:time:invertedPendulumController

8 {

9  invertedPendulumController.jitter = time64.rand_uniform(0us,500us); /* input jitter */

10  invertedPendulumController.deadline = 8ms;

11  invertedPendulumController.priority = 1; /* priority if needed, here only one process it is not applicable */

2  invertedPendulumController.execution_time = time64.rand_uniform(0us,2000us); /* input to output delay */

13 }

```

**Figure 5.** Snippet of CPAL code instantiating a controller of period 10 ms and offset 2 ms and specifying the variation of the input jitter  $J^h$  and the input-to-output delay  $\tau$  during a simulation run. This is achieved through a timing annotation executed in simulation, but ignored once on target.

The implementation is discrete-event based simulation using Simulink built-in zero-crossing 280 detection. The concept of tasks and real-time schedulers are available natively in CPAL. The default 281 CPAL scheduling policy is FIFO, but CPAL also supports Non-Preemptive Earliest Deadline First 282 (NP-EDF) and Fixed Priority Non-Preemptive (FPNP). In Figure 5, we show the instantiation of a 283 controller task and the task parameters with the delays and jitters. A timing annotation can also specify 284 the scheduling policy if the controller consists of several tasks. Simulation of the plant dynamics 285 is carried-out by computing model states at successive time steps over a specified duration. This 286 computation is done by a solver provided in Simulink. Since our overall model is discrete, a variable 287 step size solver is used in our co-simulation approach. The rationale behind this choice is that for the 288 timing analysis of real-time control systems, it is necessary to reduce the step size (when needed) to 289 increase the accuracy when model states are changing rapidly during zero crossing events. Section 5.1 290 presents an example co-simulation of a simplified cruise control system. 291

## 292 4. Timing Verification Using Schedulability Analysis

The next step in the framework is the timing verification of the controller model designed in the previous step. From the jitter margins, we derive the deadlines of the controller task(s). Typically it will be a single task, but the controller can also be implemented as several tasks such as an input task, a computation task and an output task. The deadlines will be used for the scheduler synthesis and schedulability analysis. To obtain realistic Worst-Case Execution Times (WCET) for the schedulability analysis, we use a measurement-based technique in which the controller model is executed on the target hardware.

## 300 4.1. Worst-Case Execution Time (WCET) Measurement

The CPAL controller model which we executed earlier in the co-simulation environment 301 is now uploaded to the target platform to estimate the WCET by measurements. The CPAL 302 model-interpretation engine is specific to a target platform, it can be executed on top of an Operating 303 System (OS) or without an OS, the latter being called Bare-Metal Model Interpretation (BMMI). There 304 are two ways to estimate the WCETs: using a logic analyzer or taking advantage of CPAL in-built 305 execution-time measurement feature. The latter possibility is only available when CPAL is hosted by an 306 307 OS, as freeRTOS, embedded Linux or Raspbian. It does not require connecting the target to an external measurement device and instrumenting the code, and thus provides a quick method to estimate the 308 WCET. It is however less accurate than measurements using logic analyzer, since it involves additional 309 run-time overhead in the interpretation engine. 310

For the discrete-time PID controller used in Section 5, the measured WCET of the CPAL controller 311 task using logic analyzer is 34.4  $\mu$ s on a Raspberry Pi2 model B. This can also be obtained using the 312 in-built feature of CPAL --stats, a command-line option to be used when we execute the model on target. When we remove the code of the actual control algorithm, leaving just the skeleton of the 314 tasks, we can observe the scheduler overhead, which amounts to 155  $\mu$ s. When we execute the model 315 as it is, we observe the scheduler overhead plus the execution time of the task to be 189  $\mu$ s. The 316 difference between these two values would then provide the execution time of the task, 34  $\mu$ s, which is 317 indeed observed also on the logic analyzer. With an ARM Cortex-A7 core at 900 MHz, Raspberry Pi is a cost-effective development platform to experiment with CPAL but it is not suited for executing 319 real-time applications due to large timing variabilities (e.g., jitters in task release times). The best 320 supported platform with respect to timing predictability is the NXP FRDM-K64F, a SOC on which the 321 CPAL execution engine runs on the bare hardware, thus without any interference and latency from an 322 OS. As provided in the supplementary files (both WCET measurement and jitter measurements), we 323 experiment the same controller model on FRDM-K64F target too, which is a BMMI target. Despite 324 BMMI, due to inferior hardware configuration, we observe that the same task takes 340  $\mu$ s to execute 325 on the FRDM-K64F, about 10 times more than on the Raspberry Pi. We present the model on target 326 experiments of Section 5 with Raspberry Pi because we could output the jitter measurements on the 327 console at run-time through process introspection features. CPAL on FRDM-K64F does not have a 328 facility to provide console outputs. In this case, a logic analyzer helps us to monitor the model executed 329 on the target. 330

Deriving safe and precise WCET bounds is a difficult issue in itself (see [21] for a survey), and 331 determining WCET estimates using state-of-the-art techniques and tools is outside of the scope of 332 this work. Although it is a practical approach widely employed in the industry, using measurements 333 as done in this work carries the risk of being unreliable because the worst-case situation might 3 34 not have been observed. This becomes especially true for complex systems, with many tasks and 335 architectures including multiple cores and multiple levels of caches. In such settings, more advanced 336 WCET estimation techniques must be employed. Our framework would however work with any 337 other WCET estimation techniques such as static deterministic analysis or probabilistic analysis. For 338 339 instance, it is possible on the basis of the measurements to provision for a safety margin, typically using probabilistic arguments [22]. This margin can for instance account for cache latencies which 340 have not been considered here. Another option is to employ an analytic WCET analysis, generally 341 considered safer than measurement-based techniques, although much more conservative. 342

#### 343 4.2. FIFO Scheduling to Simplify Design and Verification

We are interested in devising an environment that eases the design and verification of embedded 344 real-time systems. A main goal is to provide an environment where also the inexperienced designers 345 are able to quickly model and deploy trustworthy embedded systems without for instance having to 346 master real-time scheduling theory and resource-sharing protocols. Especially corner case faults due 347 to different timing behaviors or race conditions can be a nightmare to debug. We acknowledge that 348 techniques to avoid these problems exist, but they require experience and make both the design and 349 the code more complex and error-prone. When processing power is sufficient other concerns than 350 performance, such as simplicity and predictability, can be considered. In our context, as shown in [13], 351 FIFO exhibits two properties which greatly eases the verification: 352

Deterministic execution order: the execution order of FIFO scheduling with offset and strictly periodic task activation is uniquely and statically determined. This means that whatever the execution platform and the task execution times, be it in simulation mode in a design environment or at run-time on the actual target, the task execution order will remain identical. Beyond the task execution order, the reading and writing events that can be observed outside the tasks occur in the same order. This property, leveraged by the CPAL design flow [16], provides a form of timing

359

360

equivalent behavior between development and run-time phases which eases the implementation of the application and the verification of its timing correctness.

Execution time sustainability: FIFO scheduling is sustainable in the tasks' execution times, meaning that if a task set is deemed schedulable and the execution times of the tasks are reduced, the task set remains schedulable.

The latter property allows simulation as a valid technique for schedulability verification. In 364 practice, however, the simulation time required can be unpractical if the least-common multiple of the 365 task periods is too large. A schedulability analysis does not suffer from this limitation. In this context, 366 we derive a schedulability analysis for FIFO scheduling on uniprocessor systems with strictly periodic 367 task activation and tasks having release offsets. It should be noted that the use of offsets is a technique 368 which increases the ability of FIFO to meet deadlines, no matter if the offset of a task is unique as in 369 this work (see the experiments in [13]) or may vary, as in [23]. With offsets, FIFO becomes a candidate 370 scheduling policy for low-memory embedded hardware with constrained run-time overheads. 371

We proposed in [12] a scheduling synthesis approach, where performance, hardware and functional constraints only need to be specified to derive a feasible low-level scheduling configuration. The framework proposed in this paper is compatible with any scheduling policy that guarantees that the deadlines will be met, although in the remainder of this paper, we will rely on FIFO which, as explained, facilitates the system design.

#### 377 4.3. FIFO Schedulability Analysis

Here we present an analysis to check that the tasks will always terminate before their deadline. In the case of strictly periodic release, the release time  $r_i^j$  of job  $T_i^j$  is given by

$$r_i^j = O_i + jh_i \tag{3}$$

and its absolute deadline  $d_i^j$  by

$$d_i^j = O_i + jh_i + D_i. aga{4}$$

$D_i$  is the relative deadline,  $h_i$  is the task's period and  $O_i$  is the task's offset. Even though we are not aware of any prior work on FIFO scheduling with offsets, we were able to construct a schedulability analysis for this policy using already established schedulability results, in particular, the schedulability test for EDF with offsets presented by Pellizzoni and Lipari [24].

We note that FIFO is work-conserving in the sense that it does not introduce any idle times when 382 work is pending. This means that prior to any deadline miss, there must be a busy period in which 383 the processor is not idling. As we assume arbitrary offsets and strictly periodic releases, we do not 384 know when a deadline-miss happens and so, would need to validate all busy periods within twice the 385 hyperperiod. To avoid this prohibitively long search, we construct for each task, a hypothetical critical 386 instant leading to a task's first deadline miss. Let  $\tau_i$  be the task to miss its deadline, and  $\tau_i'$  released 387 at  $r_i^j$  the corresponding job. The critical instant happens when all tasks other than  $\tau_i$  release a job as 388 close to  $r_i^j$  as possible. If we can prove that despite this pessimistic assumption, job  $\tau_i^j$  will finish before 389 its deadline  $d_i^j$ , we can conclude that no job of task  $\tau_i$  will ever miss its deadline. If we can repeat the 390 same argumentation for each task in  $\Gamma$ , we can conclude that the complete task set is schedulable. 391

Formally, we define for each task  $T_i$  a pseudo task-set  $\hat{\Gamma}$  that represents the critical instant for task  $T_i$ . The two task sets  $\Gamma$  and  $\hat{\Gamma}$  only differ in the task offsets, the rest of the parameters remaining identical. Let  $\hat{T}_i^j$  be a job that misses its deadline. As we know that in a work-conserving scheduling algorithm, a deadline miss must be within a busy-period L, we set the release time as follows  $\hat{r}_i^j = L$ and its deadline to  $\hat{d}_i^j = L + D_i$ . George et al. [25] presented a bound based on the task deadline and the utilization of the task set:

$$L_{U} := \max_{i} \left\{ D_{1}, D_{2}, \dots, D_{n}, \frac{\sum_{i=1}^{n} (h_{i} - D_{i}) U_{\Gamma}}{1 - U_{\Gamma}} \right\}$$

(5)

Ripoll et al. [26] presented a bound based on the following recursive equation:

$$L_{R}^{a+1} := \sum_{i=1}^{n} \frac{L_{R}^{a}}{h_{i}} C_{i}$$

(6)

Since both bounds  $L_R$  and  $L_U$  are independent, we can take the minimum of both as the task set's busy period *L*:

$$L := \min\{L_R, L_U\} \tag{7}$$

<sup>397</sup> Naturally, the busy period is only bounded if the task set utilization  $U_{\Gamma}$  is less than or equal to one.

We now select the task parameter of each task  $\hat{T}_l$  with  $l \neq i$  to maximize the likelihood of a deadline miss of job  $\hat{T}_i^j$ . To this end, we postpone the job release of the last job of task  $\hat{T}_l$  executed before the deadline miss as much as possible. An earlier job release will only increase the slack time and so, reduce the pressure on the finishing time of job  $T_i^j$ .

In case of a higher priority task, *i.e.*,  $\hat{T}_l$  with l < i, the job must be released just before or synchronously with  $\hat{T}_i^j$ , whereas tasks with lower priority must be released strictly before  $\hat{T}_i^j$ . Since we use task priorities as a tie breaker, a lower priority task released synchronously with  $\hat{T}_i$  would be executed after, and not before task  $\hat{T}_i$ . Pellizzoni and Lipari presented a computation of the minimum distance between any two release times of two different tasks  $T_i$  and  $T_l$ . In contrast to their work, we are not only interested in the minimal distance, but also in the minimal distance larger than zero. We therefore repeat the computation of the minimal distance.

Let  $\delta$  be distance between *j*th job of task  $T_i$  and the *k* job of task  $T_l$ :

$$\delta_{i,l} = j \cdot h_i + O_i - k \cdot h_l + O_l \tag{8}$$

By replacing  $h_i$  with  $x_i \cdot \text{gcd}(h_i, h_l)$  and  $h_l$  with  $x_l \cdot \text{gcd}(h_i, h_l)$ , we get

$$\delta_{i,l} = j \cdot h_i + O_i - k \cdot h_l + O_l$$

$$j \cdot x_i \cdot \gcd(h_i, h_l) + O_i - k \cdot x_l \cdot \gcd(h_i, h_l) + O_l$$

$$(j \cdot x_i - k \cdot x_l) \gcd(h_i, h_l) + O_i - O_l$$

Since  $j \cdot x_i - k \cdot x_l$  can take any arbitrary value, we replace it by x and get

$$\delta_{i,l} = x \cdot \gcd(h_i, h_l) + O_i - O_l \tag{9}$$

Now, we just need to find the smallest  $\delta_{i,l} \ge 0$  and the smallest  $\delta_{i,l} \ge 1$ , which are given by

$$x = \frac{O_l - O_i}{\gcd(h_i, h_l)}$$

and

$$x' = \frac{O_l - O_i + 1}{\gcd(h_i, h_l)}$$

Applying these values to Equation (9), we get

$$\Delta_{i,l} = O_i - O_l + \left\lceil \frac{O_l - O_i}{\gcd(h_i, h_l)} \right\rceil \gcd(h_i, h_l).$$

<sup>(10)</sup>

and

$$\Delta_{i,l}' = O_i - O_l + \left\lceil \frac{O_l - O_i + 1}{\gcd(h_i, h_l)} \right\rceil \gcd(h_i, h_l).$$

(11)

Finally, we can set the release time of the last job  $\hat{T}_l^k$  of task  $\hat{T}_l$  executed before  $\hat{T}_i^j$  as follows:

$$\hat{r}_{l}^{k} = \begin{cases} \hat{r}_{i}^{j} - \Delta_{i,l} & \text{if } l \leq i \\ \hat{r}_{i}^{j} - \Delta_{i,l}^{\prime} & \text{if } l > i. \end{cases}$$

$$(12)$$

The offset of task  $\tau_i$  is given by

$$\hat{O}_i = \hat{r}_i^j \mod h_i, \tag{13}$$

and for all other tasks  $l \neq i$  by

$$\hat{O}_l = \hat{r}_l^k \mod h_l. \tag{14}$$

The remaining task set parameters, *i.e.*, the relative deadline, period and execution time remain unchanged.

It is sufficient to validate the schedulability of  $\hat{\Gamma}$ : if  $\hat{T}_i$  in  $\hat{\Gamma}$  is schedulable with FIFO, so is  $T_i$  in  $\Gamma$ . Furthermore, since we know which job of task  $\hat{T}_i$  will miss its deadline in case of a deadline miss, it is sufficient to concentrate on the *j*th job  $\hat{T}_i^j$ , which allows us to reduce the analysis time. If we are able to prove or disprove a deadline miss of job  $\hat{T}_i^j$ , we can immediately abort the schedulability analysis of task  $T_i$ . Consequently, we concentrate only on job  $\hat{T}_i^j$  and ignore all others. First, we define the number of job releases that may postpone the completion of task *i* within a given time interval.

The function  $\eta_l^{inc}(t_1, t_2)$  denotes the number of job releases of task  $\tau_l$  within the time interval  $[t_1: t_2]$ , *i.e.*, including  $t_2$  and is given as follows:

$$\eta_l^{inc}(t_1, t_2) = \left\lfloor \frac{t_2 - \hat{O}_l}{h_l} \right\rfloor + 1 - \left\lceil \frac{t_1 - \hat{O}_l}{h_l} \right\rceil$$

(15)

The function  $\eta_l^{exc}(t_1, t_2)$  denotes the number of job arrivals of task  $\tau_j$  within the time interval  $[t_1: t_2)$ , *i.e.*, excluding  $t_2$  and is given as follows:

$$\eta_l^{exc}(t_1, t_2) = \left\lceil \frac{t_2 - \hat{O}_l}{h_l} \right\rceil - \left\lceil \frac{t_1 - \hat{O}_l}{h_l} \right\rceil$$

(16)

Using these two functions, we define the processor demand *PD* within time interval  $[t_1: t_2]$  that can delay the completion of a job of task  $\hat{T}_i$  released at  $t_2$ :

$$PD(t_1, t_2, i) = \sum_{l \le i} \eta_l^{inc}(t_1, t_2) \cdot C_l + \sum_{l > i} \eta_l^{exc}(t_1, t_2) \cdot C_l$$

(17)

Again, we distinguish between tasks with higher priorities and tasks with lower priorities to correctly

account for the tie-breaking policy in case of synchronous job arrivals.

We can test for a deadline miss of job  $\hat{T}_i^j$  as follows:

$$\forall t \in [0: \hat{r}_i^j, i]: PD(t, \hat{r}_i^j, i) \le \hat{d}_i^j - t \Rightarrow \hat{f}_i^j \le \hat{d}_i^j$$

(18)

To reduce the number of test, we observe that  $PD(t_1, t_2, i)$  only changes at the time of a job release, which means that we only need to validate the schedulability at these points:

$$Q = \{t | \exists l, k \colon t = k \cdot h_l + \hat{O}_l \land t \le L - D_i\}$$

$$\tag{19}$$

Hence, we can validate the schedulability of task  $T_i$  as follows:

$$\forall t \in Q \colon PD(t, \hat{r}_i^j, i) \le \hat{d}_i^j - t \Rightarrow \hat{f}_i^j \le \hat{d}_i^j$$

(20)

We note that the schedulability test is sufficient but not necessary, and does not provide an equivalence between the schedulability of  $\Gamma$  and  $\hat{\Gamma}$ . The schedulability analysis can falsely deem a schedulable task set unschedulable, but not the inverse.

From Equation (20), we find the worst-case finishing time of the task  $T_i$

$$\hat{f}_i = \max_{\forall t \in Q} \{ PD(t, \hat{r}_i^j, new) + t \}$$

(21)

Then the worst-case response time of a task  $T_i$  is  $R_i^w$

$$R_i^w = \hat{f}_i - \hat{r}_i \tag{22}$$

Algorithm 1 Worst-Case Response time  $R_i^w$ 1: i = 1

2: isSchedulable = true 3: L = computeBusyPeriodwhile  $i \leq n \land$  isSchedulable **do** 4:  $\hat{r}_{i}^{J} = L$ 5:  $\hat{O}_i = r_i^j \mod h_i$ 6: for all do 7:  $d\hat{i}st_{i,l} = \text{computeMinDistance}(i, l)$ 8:  $\hat{O}_l = r_i^l - \hat{dist}_{i,l} \mod h_i$ 9: 10: end for  $Q = \{t | \exists l, k \colon t = k \cdot h_l + \hat{O}_l \land t \leq L\}$ 11: 12: for all  $t \in Q$  do if  $PD(t, \hat{r}_i^j, i) - t > \hat{d}_i^j$  then isSchedulable = false 13: 14: end if 15: if ¬isSchedulable then break end if 16:  $\hat{f}_i^j = \{PD(t, \hat{r}_i^j, i) + t\}$ 17: 18: end for  $\hat{f}_i = \max{\{\hat{f}_i^j\}}$ 19:  $R_i^w = \hat{f}_i - \hat{r}_i$ 20: 21: i = i + 122: end while 23: return isSchedulable 24: return  $R_i^w$

Algorithm 1 consolidates the analysis presented so far. Using this algorithm, we can derive the 424 worst-case response times of all task. To check schedulability, we verify that these response times are 425 less than or equal to the fine-tuned deadlines, which we have obtained from the previous step. To 426 achieve transparency and to ease the reproduction of the results, the source code of the programs used 427 in our experiments, including the schedulability test, is available online<sup>1</sup>. The source code enables the 428 reproduction of the experiments presented in this paper, as well as evaluation for different parameters 429 settings. The tool *cpal2x* (see [17] for usage), which is available in the CPAL distribution, extracts the 4 30 timing information (timing and scheduling annotations) from the controller function designed at step 1. 4 31 This constitutes the system task model which is then inputted to the presented schedulability analysis. 4 3 2

<sup>&</sup>lt;sup>1</sup> https://www.designcps.com/wp-content/uploads/cpal\_codesign\_framework.zip

#### 433 5. Evaluation and Results

We now evaluate the framework with the help of an automotive control system. Before presenting 4 34 the evaluation, we describe the system model. As depicted in the framework of Section 2, the evaluation 4 35 consists of three steps. Firstly, we calculate the tolerable jitter margin values under which the system 436 remains stable using jitter margin analysis. The calculated output jitter margin provides the maximum 437 deadline for the controller task. This deadline is further fine-tuned using co-simulation that provides 4 38 additional and more fine-grained information about the control performance. Secondly, we evaluate 439 the schedulability of the controller task when executed with other tasks in the system. Finally, in 440 the third step, we use CPAL introspection to check that the run-time behavior of the controller task 441 complies with the design assumptions. 442

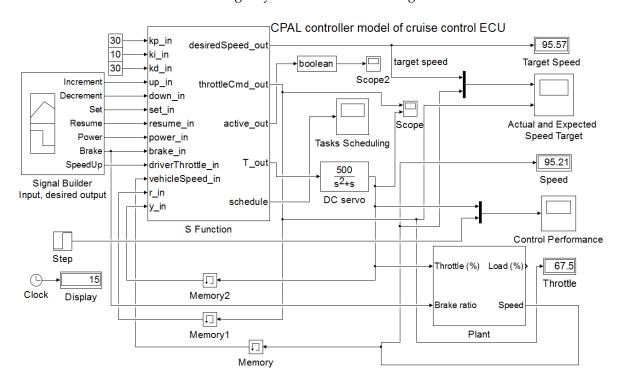

## 443 5.1. Motivating Example : Cruise Control ECU

A Cruise Control system maintains the speed of a car at a desired level. For that, the system 444 uses a servo mechanism that takes over the throttle of the car to maintain a steady speed as set by the 445 driver. The system model used is taken from the Simulink reference examples [27], but the controller 446 model is replaced by a CPAL implementation. Without injecting run-time delays, both the CPAL 447 implemented version of the controller and the Simulink version provide the same outputs. This 448 comparison is available in the supplementary files provided. Figure 6 shows the architecture of the 449 co-simulation model. The proposed co-simulation environment provides the control performance 450 with the run-time delays due to execution times and interferences from higher priority tasks, and 4 5 1 facilities the visualization of the task scheduling. In addition, the same controller model developed for 452 simulation can be executed on the target by the CPAL execution engine. 453

**Figure 6.** Illustration of a CPAL controller in Simulink. Here, the CPAL model controls the servo which in turn actuates the engine throttle. The controller task is executed with simulated input-to-output delays.

In our implementation, different tasks and variables are defined within the controller model. We consider tasks, namely *set point manager*, *cruise control manager* and *sensors manager*. The label *T\_out* in Figure 6 is the controller tasks' output which actuates the DC servo mechanism controlling the throttle valve. We model the DC servo with the transfer function  $P(s) = \frac{500}{(s^2+s)}$ . The controller developed relies on a PID control algorithm with proportional gain  $K_p = 0.96$ , derivative gain  $K_d = 0.049$ , integral gain  $K_i = 0.12$  and filter divisor N = 5.0.

460 5.2. Controller Design

The evaluation of the controller designed consists of two steps, namely the analytical jitter margin method and the co-simulation technique.

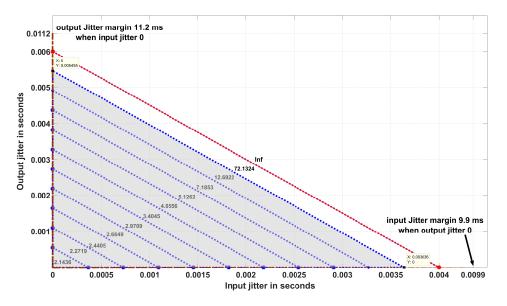

## 463 5.2.1. Step 1. a) Stability Verification using Jitter Margin Concept

For a given controller and a nominal input-to-output delay  $\mathcal{L}$ , the Jitter margin toolbox [15] 4 64 computes the tolerable level of jitter for which stability is guaranteed (like phase margin and gain 465 margin computations of control systems). This toolbox provides the stability curve that determines the 466 maximum tolerable output jitter  $J^{\tau}$  and maximum tolerable input jitter  $J^{h}$ , based on the nominal 467 input-output delay  $\mathfrak{L}$ . Figure 7 shows the worst case control cost which is a  $H_{\infty}$  (H-infinity) 468 performance metric calculated for different input and output jitters. For example, for the PID controller 469 of the previous sub-section with a sampling period of 12 ms, the nominal (minimum) input-to-output 470 delay  $\mathfrak{L}$  is equal to 5.6 ms, the input jitter margin  $J^h$  is 3.64 ms, the output jitter margin  $J^{\tau}$  is 5.45 ms, 4 71 while the control cost  $H_{\infty}$  is 72.13 ms. The input-to-output delay, which is the sum of encountered 472 jitters during the execution of the controller task is then 9.09 ms. The control cost we use is  $H_{\infty}$ , a gain 473 parameter calculated when we apply a disturbance input to the plant and the corresponding output 474 amplifies. 475

**Figure 7.** The worst-case control cost calculation during various input and output jitter occurrences. The control cost mentioned here is  $H_{\infty}$ , a gain parameter. Finite control costs indicate that the system is stable while an infinite value '*Inf*' indicates that the system tends to be unstable. At zero input and zero output jitter, the highest performance is achieved. The control cost increases when jitters increase.

When we get a finite value for the gain parameter  $H_{\infty}$ , it indicates that the system remains stable. Beyond the jitter margin, we observe that the gain becomes infinite, which means that the system tends to be unstable. During the ideal situation where the controller task executes with zero input jitter and zero output jitter, we obtain the highest possible control performance with control costs  $H_{\infty}$  equal to 2.14. If we want to guarantee a certain control performance, expressed in terms of  $H_{\infty}$ , we have to design the system such that the experienced jitters are within the jitter margins leading to  $H_{\infty}$  being no greater than the target. For instance in Figure 7, the jitters must remain in the shaded region to ensure that  $H_{\infty}$  remains equal to 72.13. This allows to deduce that the controller task deadline must be less than 9.09 ms. Now, to fine-tune the deadline and also to study the effect of scheduling choices on the control performance, the co-simulation approach is used. In the implementation of the cruise-control system, the controller task, denoted *Task* 1, is activated every 12 ms. *Task* 2 is another task with the same period, always activated before *Task* 1. In case both are released at the same time, the execution time generates an input jitter for *Task* 1. This latency, plus the varying execution time of *Task* 1 itself, induce the output jitter.

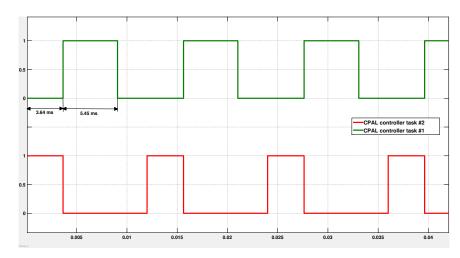

**Figure 8.** Successive activations of two tasks under FIFO. *Task* 1 is the controller we design with a period of 12 ms. *Task* 2 is the *cruise control manager* also with a 12 ms period. As *Task* 2 is of higher priority, it is activated first when both tasks are released simultaneously. Using varying execution time annotations for *Task* 1 and *Task* 2, we enforce an input-to-output delay of at most 9.09 ms for *Task* 1, which is the bound obtained from jitter margin analysis.

Figure 8 illustrates the execution of the tasks under First-In First-Out (FIFO) policy. As we can see from Figure 8, *Task* 1, the controller under design, experiences an input jitter of 3.64 ms. This is realized by means of an execution time annotation (see Section 3.3) of an interfering task activated immediately before. By setting the execution time of *Task* 1 to 5.45 ms, combined with the input jitter, we enforce an input-to-output delay of 9.09 ms. This is the tolerance level beyond which the system performance degrades significantly, as shown in Figure 9.

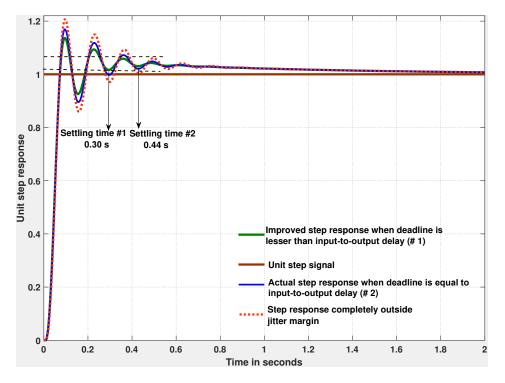

## 5.2.2. Step 1. b) Co-simulation CPAL/Simulink

The co-simulation of CPAL in the Simulink environment serves two purposes: fine-tuning of the 497 deadline and selection of the scheduling policy. Although the jitter bound derived by jitter margin 498 analysis helps to assign the deadline, in practice a system designer may want to evaluate the control 4 9 9 performance with the response to an input elementary signal such as impulse or a step signal. For 500 this purpose, we feed an unit step signal in the co-simulation model to study the step response of the 5 01 system. Based on the step response characteristics such as rise time, settling time and overshoot, we 502 can decide whether a fine tuning of the deadline is necessary. For instance, if the control requirement 503 is to achieve a desired settling time, defined as the time taken to settle within 2% of the steady state value, equal to 0.3 s, then the deadline should be no greater than 8.2 ms (versus 0.44 s with a deadline 5 0 5 of 9.09 ms). In our previous work [5], we have exemplified the co-simulation of CPAL in Simulink to 506 study the control system performance for different scheduling options. 507

**Figure 9.** Control performance using step response for different deadline assignments: equal, less and greater than the input-to-output delay (resp. blue, green and red curves). The green curve (reduced overshoot one) is obtained with a deadline value equal to 8.2 ms chosen such that the settling time within 2% of the steady-state value is less than 0.3 s. When the control task deadline is greater than the jitter margin, logically the system performs poorer with increased oscillations and overshoots.

#### 508 5.3. Step 2) Software Design

As explained earlier in Section 4.1, the controller model we designed at step 1 is now uploaded 509 on the target platform to estimate a WCET bound. For the specifications of the controller with the 510 sampling period of 12 ms (see Section 5.1), the execution time of the CPAL controller task measured using a logic analyzer is 34.4  $\mu$ s. As explained in Section 4, WCET estimation can also be conveniently 512 performed using the CPAL in-built --stats feature. For the controller task developed, the maximum 513 execution time value observed is around 200  $\mu$ s including the scheduler overhead. When there are 514 no preemptions as here, or a bounded number of preemptions, it is possible to include the scheduler 515 overhead in the WCET of the task. To provision for a safety margin, we consider the execution time along with the scheduler overhead. We use this WCET and the admissible deadline of 8.2 ms obtained 517 from the previous step to test the schedulability of the system. The schedulability analysis presented in 518 Section 4.3 tells us whether the integrated task set (the controller under design plus the existing tasks 519 on the ECU) is feasible or not. In our experimental setup, the task set passes the schedulability test. 520

Once we obtain a stable controller model, we verify its run-time behavior on the target hardware. 521 At run-time, it is possible in CPAL for a process instance to query its id, period, offset, both input 522 and output jitters, priority, deadline and the activation times of the current and previous activations. 523 Statistics can be collected and analyzed off-line, but it is also possible to visualize at run-time the 524 variation of these quantities. Figure 10 shows a snippet of the code of the two monitoring tasks of 525 Task 1, one for the input jitter and one for the output jitter, as well as their scheduling parameters. 526 Here the choice has been made to have external tasks monitoring the jitters in order to not clutter the 527 controller code. Although FIFO is the scheduling policy, simultaneous task releases are broken with 528 the *priority* attribute (see Figure 10). 529

```

IO.sync();

IO.println("id %u input jitter %t Priority %u Period %t Offset %t", p.pid,

[p.current_activation - p_mon_init.current_activation, p.priority, p.period,

IO.println("id %u output jitter %t Priority %u Period %t Offset %t", p.pid,

itter %t Priority %u Period %t Offset %t", p.pid,

p.offset);

self.current_activation - p.current_activation - p.bcet, p.priority, p.period, p.offset);

pin = false;

I0.sync();

}

@cpal:time{

p2_mon_in.priority = 6;

p2_mon_in.offset = 0ms;

p2.priority = 5;

p2.offset = 0ms;

p2.period = 12ms

p2_mon_out.priority = 4;

p2_mon_out.offset = 0ms;

p1_mon_in.priority = 3;

p1_mon_in.offset = 0ms;

pl.priority = 2;

pl.offset = 0ms;

pl.period = 12ms

pl_mon_out.priority = 1;

pl_mon_out.offset = 0ms;

system.sched_policy = Scheduling_Policy.FIF0;

pi@raspberrypi:~/Downloads/CPAL_121 $ sudo chrt 60 ./cpal_interpreter_raspberry -r -t 10000 -q observer.ast

setup

=> Digital pin found: 0, output

=> Digital pin found: 1, output

=> Digital pin found: 2,

output

=> Digital pin found: 3, output

=> Digital pin found:

4, output

=> Digital pin found: 5, output

[2137952.756385186000:PRINTLN] id 0 input jitter 133us177ns Priority 5 Period 12ms Offset 0

[2137952.754930812000:PRINTLN] id 0 output jitter 162us396ns Priority 5 Period 12ms Offset 0

[2137952.755765551000:PRINTLN] id 1 input jitter 1ms441us561ns Priority 2 Period 12ms Offset 0

[2137952.756385186000:PRINTLN] id 1 output jitter 116us510ns Priority 2 Period 12ms Offset 0

```

Figure 10. Code snippet of the two monitoring processes, including their scheduling parameters.

530 5.4. Step 3) Introspection Features for Run-time Verification

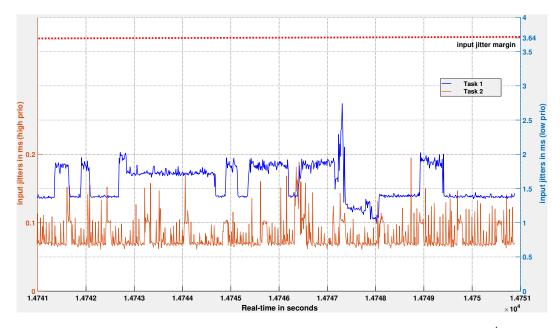

**Figure 11.** Global view of input jitter measurements of *Task* 1 and *Task* 2. The input jitter  $J^h$  of *Task* 1 (blue curve, right y-axis) varies over time below 2 ms, except in rare cases where it reaches 2.7 ms. The input jitter of *Task* 2 (red curve, left y-axis) is bounded by 0.2 ms. The design assumption of input jitters for *Task* 1 is less than 3.64 ms is met by the implementation.

During model on target execution, the run-time monitoring tasks are respectively executed before 5 31 the start of the controller task and immediately after. This can be for instance ensured by setting the 5 3 2 priority attribute so that the input-monitoring process is at a higher priority than the controller task (3 in our case), while the output-monitoring task is at the immediate lower priority (1 in our case). 5 34 The controller Task 2 is the cruise control manager of higher functional importance. It is activated first 535 when both *Task* 1 and *Task* 2 are released simultaneously. The lower part of Figure 10 shows a sample 536 console display of the input and output jitters during command-line execution in real-time mode 537 (i.e. option -r in the command line) of the CPAL controller model with quiet option -q enabled. Here, jitters are recorded for 10 seconds on a Raspberry Pi2 model B with an ARM Cortex A7 processor. 5 3 9

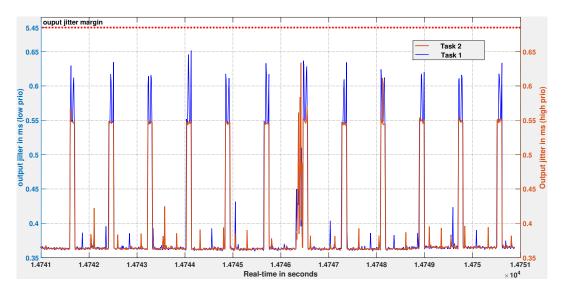

Figure 11 shows the input jitter measurements of the two controller tasks, *Task* 1 and *Task* 2, over a duration of 10 seconds. Even if *Task* 1 suffers delays from *Task* 2, we observe that its input jitters are well within the input jitter margin value of 3.64 ms (see Section 5.2.1). Likewise, Figure 12 shows the output jitter measurements for both controllers, and the cruise-control system meets the 5.45 ms output-jitter margin. These experiments, along with logic analyzer measurements confirm the design assumptions related to jitters. The logic analyzer set-up and captures files are available as additional references within the supplementary files provided with this article.

**Figure 12.** Global view of output jitter measurements of *Task* 1 and *Task* 2. The output jitter  $J^{\tau}$  of *Task* 1 (blue curve, left y-axis) varies over time but remains below 0.65 ms. The output jitter of *Task* 2 (red curve, right y-axis) is bounded by 0.63 ms. The design assumption of output jitters for *Task* 1 is less than 5.45 ms is met by the implementation.

We enabled -q (quiet) option during model execution to get only the necessary console outputs, 547 which are the jitter values during run-time. We record these jitter values for the purpose of visualization 548 and to study whether the jitters are within the margins. To cross-check, we also measure the jitters 549 using a logic analyzer with a 100 MHz sampling rate for about 10 seconds, as shown in Figure 13. For 550 a particular job instance (zoomed portion of the figure), we measure an execution time of 34.58  $\mu$ s 551 for controller Task 1 and 25.19 µs for controller Task 2, which both run with a period of 12 ms. The 552 monitoring processes (input and output) are here to help measure the input jitters, output jitters and 553 input-to-output delay. We observe that when we do not include the printing of jitter values on the 554 console, both input monitor and output monitor tasks (i.e. channels 1, 3 for Task 2 and channels 5, 7 for 555 Task 1) consume less than 4  $\mu$ s. Note that these monitoring tasks can be removed for the production 556 code once the design is finalized to avoid overhead. 557

## Version February 8, 2018 submitted to Sensors

**Figure 13.** The input and output monitoring task activations for two controller tasks captured using a logic analyzer. Both the controller tasks *Task 1, Task 2* are activated with a period of 12 ms. Both are different control algorithms which run for an execution time of 34.58  $\mu$ s and 25.19  $\mu$ s, respectively at the highlighted job instant. The monitoring tasks execute only a fraction of the controller's computation time, typically less than 4  $\mu$ s

## **558** 6. Related Works

In the literature of computing and control, there have been numerous studies on the effects of timing irregularities on control performance [2–5]. Cervin et al. coined the term *jitter margin* in [28], where the authors considered the output jitter margin under which the system still maintains its stability. In a subsequent work [15], Cervin extended the analysis to account for both the input and output jitters on the control performance of linear sampled-data control systems. In this paper, we integrate this analysis in a tool-supported design flow which guarantees the control performance on a given execution platform.

A technical contribution needed in this work is a FIFO schedulability analysis for periodic tasks with offsets. Closely related are the results by George and Minet published in [29], who proposed a scheduling analysis for FIFO on a distributed system assuming sporadic task releases, and the results by Leontyev and Anderson [30], who developed a tardiness analysis for FIFO scheduling of soft real-time tasks, also assuming a distributed system and sporadic task releases. The two latter works did not apply directly to our task model, i.e., periodic task with release offsets.

Sangiovanni-Vincentelli et al. discussed various methodologies to address the system design 572 challenges in [31]. This work highlights the importance of Assume/Guarantee contracts during 573 component design and explains how a contract can be applied to the design of a water flow control 574 system. Derler et al. proposed in [7] that implicit timing assumptions are made explicit using design 575 contracts to facilitate the interaction and communication between control and software domains. 576 The authors discussed the support for timing-contracts-based designs using Ptolemy and Simulink. 577 Benveniste et al. proposed in [32] to apply contracts to design methodologies. Importantly, the authors 578 explained the mathematical concepts and operations necessary for the contract framework. All these 579 works mentioned in this paragraph focused on the fundamental framework for design contracts, 580

such as contract algebra applied in system design, and timing contract visualization in modeling

environment. In this work, we are concerned with the application of timing tolerance contract in

our Model-Based Design flow used to develop control software, thus focusing on scheduling and

implementation issues.

In terms of related design environments, we identify two approaches with associated tools aiming to support control system design considering the influence of scheduling strategies:

• TrueTime: this MATLAB/Simulink-based tool [2] enables the simulation of the temporal behavior 58 of controller tasks executed on a multitasking real-time kernel. In TrueTime, it is possible to 588 evaluate the performance of control loops subject to the latencies of the implementation. TrueTime 580 offers a configurable kernel block, network blocks, protocol-independent send and receive blocks 590 and a battery block. These blocks are Simulink S-functions written in C++. TrueTime is an 591 event-based simulation using zero-crossing functions. The tasks are used to model the execution 5 92 of user code and are written as code segments in a MATLAB script or in C++. It models a number 5 9 3 of code statements that are executed sequentially. 5 94

*T-Res*: this more recent tool [4] is also developed using a set of custom Simulink blocks created to simulate timing delays dependent on code execution, scheduling of tasks and communication latencies, and verifying their impact on the performance of control software. T-Res is inspired from TrueTime and provides a more modular approach to the design of controller models enabling to define the controller code independently from the model of the task.

These tools and methods focus on simulation and analysis. They both help the designer to study 600 the control system performance under the effects of timing delays. The system designer then takes 601 simulation analysis results into account to develop the embedded control algorithms in the next steps. 602 This increases the possibility of distortions between the simulation model and the implementation. 603 An advantage of our co-simulation modelling approach is that the same controller model used to 604 evaluate the control performance during design phase can be re-used directly on the target hardware 605 (in the coding and testing phase) to implement the system. As discussed in our previous work [5,19], 606 the reduced development cycle favors efficient interactions between control and software engineers. 607 The reader is referred to [5] for a review of CPAL in Simulink, TrueTime and T-Res development 608 environments. 609

## 610 7. Conclusion and Future Work

The timing behavior of control tasks is a critical concern in real-time digital controllers. The delays, 611 such as input jitters, or missed executions due to temporary overload, affect system performance 612 and are to be accounted for in the design phase. Model-driven engineering has been successful for 613 capturing the functional requirements during design, but non-functional requirements such as timing 614 have been traditionally overlooked. This leads to a late verification of controller timing and, in the best 615 case, to corrections at a stage when they are costlier. This work is a contribution towards conceiving 616 a design environment for embedded control systems that capture all the necessary functional and 617 non-functional requirements, while providing analysis, simulation and run-time capabilities. 618

In this paper, we presented a framework based on timing tolerance contracts which fuses the 619 stability and scheduling viewpoints during controller design. The three steps of the framework 620 have been described: controller design verified by stability analysis and co-simulation, software 621 design verified by schedulability and WCET estimation, and lastly, the implementation checked 622 through run-time verification. The crucial advantage of our co-simulation approach based on model 623 interpretation is that the same controller model verified in the design phase can be ported directly 624 (without the need for code generation) to target hardware to implement the final system. This feature 625 will ease the deployment and the update of code on distributed nodes, for instance in Industrial 626 Internet of things (IIoT) applications. 627

To exhibit the framework flow, we have presented the scheduling viewpoint using novel FIFO schedulability analysis for periodic task activations with offsets. As future work, we plan to extend the

- <sup>630</sup> framework to other schedulability analyses using tools such as Cheddar [33] and MAST [34] to support

- <sup>631</sup> more scheduling options during scheduler synthesis. Another objective is to extend the approach

- to other important non-functional properties, foremost power consumption for next-generation

- <sup>633</sup> Cyber-Physical Systems, which will require both analysis and modeling language support.

Acknowledgments: This research is supported by FNR (Fonds National de la Recherche), the Luxembourg

National Research Fund (AFR Grant n°10053122).

Author Contributions: Authors Sakthivel M Sundharam and Nicolas Navet conceived and developed the ideas

<sup>637</sup> behind the research. Sebastian Altmeyer carried out the schedulability analysis. Sakthivel M Sundharam wrote

- the paper under the supervision of Nicolas Navet. The experiments reported in this paper have been designedand performed by Sakthivel M Sundharam and Lionel Havet. Lionel Havet provided the CPAL tooling support.

- **Conflicts of Interest:** The authors declare no conflict of interest.

## 641 Abbreviations

- <sup>642</sup> The following abbreviations are used in this manuscript:

- 643

644

- BET Bounded Execution Time contract

- CPAL Cyber-Physical Action Language

- CPS Cyber-Physical Systems

- ECU Electronic Control Unit

- FIFO First In First Out

- LET Logical Execution Time contract

- MDE Model-Driven Engineering

- PID Proportional Integral Differential

- SDLC Software Development Life Cycle

- StA Sensing to Actuation Delay

- SWC Software Component

- TOL Timing Tolerance contract

- WCET Worst-Case Execution Time

- ZET Zero Execution Time contract

## 645 References